|

|

|

Главная страница Автономные управляющие системы I Сигналы ГМС I Сигналы ОС Сброс Синхронизация Параллельный расширитель Н (D о. СО о СУ Сигналы с разделяемых расширителей Vcc ! PRN ОД Q ENA CLRN .КГМС Локальная ОС О ы N 3 > Отличительной особенностью ПЛИС семейства МАХ9000 является наличие элемента ввода-вывода (Рис. 1.33) а ГМС, Рис. 1.33. ЭВВ ПЛИС семействе МАХ9000 Управляющая шина -Vcc 0е[7 0] тГМС. clk[3 0] ena[5 0] 6 9 Vcc clr [1 0] ,- ena clrn Контроль скорости Наличие в ЭВВ тактируемого триггера позволяет по сути выполнять хранение входных или выходных данных в ЭВВ, не задействуя ресурсы МЯ Временная модель ПЛИС семейства МАХ9000 приведена на Рис.1.34и 1.35, а ее параметры в Табл. 1.14 Рис. 1.34. Временная модель ПЛИС семейства МАХ9000 tROW tLOCAL tDIN D tOIN CLK tDIN CLR tDIN 10 tDIN Toe tlAD 11ЛС ISEXP tRD tCOMB tH tPRE tCLR H FTD h tcOL Рис. 1.35. Временная модель ЭВВ ПЛИС семейства МАХ9000 tlODR tiODC tjOC tiORD tlOCOMB tlOSU tOH tlOCLR tlOFD tODl tOD2 tOD3 tZXl tZX2 tZX3 liNREG J tINCOMB . Вывод ПЛИС Таблица 1.14. Параметры временной модели семейства МАХ9000

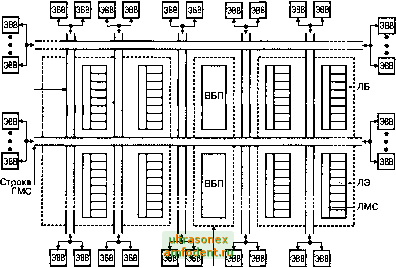

1.6. СЕМЕЙСТВО FLEX10K ПЛИС семейств FLEX10K, FLEX10KA, FLEX 10КЕ являются на данный момент, пожалуй, самой популярной элементной базой для реализации алгоритмов ЦОС, построения сложных устройств обработки данных и интерфейсов Это объясняется тем, что, благодаря большой логической емкости, удобной архитектуре, включающей встроенные блоки памяти (ЕАВ, Embedded Array Block), достаточно высокой надежности и удачному соотношению цена - логическая емкость, данные ПЛИС удовлетворяют разнообразным требованиям, возникающих у разработчика как систем ЦОС, так и устройств упрааления, обработки данных и т п В Таблице 1.15 приведены основные сведения о ПЛИС семейства FLEX10K В настоящее время выпускаются ПЛИС семейств FLEX10K с напряжением питания 5 В, FLEX10KA (V) с напряжением питания 3 3 В и FLEX 10КЕ с напряжением питания 2 5 В. Кроме того, ПЛИС семейства FLEX 10КЕ имеют емкость встроенного блока памяти 4096 бит, в отличие от ПЛИС остальных семейств, имеющих емкость ЕАВ 2048 бит. Обобщенная функциональная схема ПЛИС семейства FLEX10K приведена на Рис. 1.36 В основе архитектуры лежат логические блоки (ЛБ), содержащие 8 ЛЭ и локальную матрицу соединений Глобальная матрица соединений разделена на строки и столбцы, имеет непрерывную структуру (Fast Track Interconnect). Посередине строки располагаются встроенные блоки памяти (ЕАВ) Кроме того, имеются глобальные цепи управления, синхронизации и упрааления вводом-выводом. Встроенный блок памяти (ВБП) (Рис. 1.37) предстааляет собой ОЗУ емкостью 2048 (4096) бит и состоит из локальной матрицы соединений, собственно модуля памяти, синхронных буферных регистров, а также программируемых мультиплексоров. Сигналы на вход ЛМС ВБП поступают со строки ГМС. Тактовые и упрааляющие сигналы поступают с глобальной шины управляющих сигналов. Выход ВБП может быть скоммутирован как на строку, так и на столбец ГМС Наличие синхронных буферных регистров и программируемых мультиплексоров позволяет конфигурировать ВБП как ЗУ с организацией 256 X 8, 512 X 4, 1024 X 2, 2048 X 1. Наличие ВБП дает возможность табличной реализации таких элементов устройств ЦОС, как перемножители, АЛУ, сумматоры и ТП , имеющих быстродействие до 100 МГц (конечно, при самых благоприятных условиях, реально быстродействие арифметических устройств, реализованных на базе ВБП, составляет 10-50 МГц) Все ПЛИС семейства FLEX10K совместимы по уровням с шиной PCI, имеют возможность как последовательной, так и параллельной загрузки, полностью поддерживают стандарт JTAG Структура логического блока ПЛИС FLEX10K приведена на Рис.1.38 Сигналы на вход ЛМС поступают как со строки ГМС, так и с выходов каждого из 8 ЛЭ, входящих в состав ЛБ Таблица 1.15. Плис семейства FLEX1ОК

Рис. 1.36. Архитектура ПЛИС FLEX1 ОК Столбец ГМС

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2000 - 2025 ULTRASONEX-AMFODENT.RU.

Копирование материалов разрешено исключительно при условии цититирования. |