|

|

|

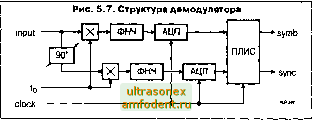

Главная страница Автономные управляющие системы > MAX+plus II - d:\mox2work\nik\3\2dlconv- [2dlconv.gdf - Graphic Editor] M*X+plusll RIe -Edif View Symbol Assign Utilities Options- Winciow Help mmmmmmmmmmi :?:j::t; ►©  4 4V f Ё г fi> а Z ЙвПуос CftMAX.plusll-d\ MAX plijG II Untillodi (?dlrnnv r.r.f Wovnlorm 1 dilot] Рис 5.6. Результаты моделирования систолической структуры на ПЛИС , шшшшшшшштшшшшятшшштшшшш Time 21 6ns Interval p 6ns 0 0ns Name. Value 111)17 0) sx(21l(7 01 x[31l[7 01 = h017 01 h1(7 01 гЬ27 0] * h3(7 0[ kSh4[7 01 h57 0 Sh6l7 01 !fh7l7 01 h8(7 0) >147 01 03 D4 D5 02 D3 D6 02 D1 D4 03 01 D2 D 101 too 0ns 2000ns iSBnycK c3>MAXtp1us1l-Unt 12.44 5.3. АЛГОРИТМЫ ФУНКЦИОНИРОВАНИЯ И СТРУКТУРНЫЕ СХЕМЫ ДЕМОДУЛЯТОРОВ Обобщенная структурная схема, по которой реализован демодулятор сигналов с частотной манипуляцией, приведена на Рис. 5.7  Как видим, используется аналоговая квадратурная обработка (перемножители, фазовращатель, фильтры нижних частот) и цифровое восстановление символов и частоты, реализованное на ПЛИС. В качестве формирователя квадратур использована ИС RF2711 фирмы RF Microdevices Данная микросхема содержит в своем составе два перемножителя и фазовращатель и позволяет работать в диапазоне частот от О 1 до 200 МГц при ширине спектра до 25 МГц. Опорная частота fo формируется с помощью синтезато ра прямого синтеза частот AD9830 [1] фирмы Analog Devices Сигнал с выхода синтезатора фильтруется с помощью активного ФНЧ, реализованного на ОУ AD8052 по схеме Рауха. В настоящее время наблюдается тенденция к оцифровыванию обрабатываемого сигнала на промежуточных частотах (ПЧ) порядка десятков МГц, формируя квадратуры в цифре . Для этих целей возможно использовать ИС AD6620 Однако это не всегда оправдано в основном из-за сложностей с управлением такой микросхемой в системах, где отсутствует собственный контроллер. В качестве АЦП удобно использовать специализированный квадратурный АЦП AD9201. Пожалуй, единственным его недостатком является необходимость демультиплексирования отсчетов синфазной и квадратурной составляющих Ниже приводится описание конструкций каждого из блоков в составе ПЛИС детектора ЧМ-сигнала и синхронизатора Определены преимущества каждой из предлагаемых схем Детектор ЧМ-сигнала предназначен для преобразования исходного модулированного радиосигнала в последовательность прямо- угольных импульсов, появляющихся с частотой следования символов и обладающих той же полярностью. Частота исходного радиосигнала равна f = fo - Af/2, если передается символ О , и f = fo + Af/2, если передается символ Г, при этом, по техническому заданию, ДТТс = 1, где Тс - длитвльность символа (индекс модуляции единица, сигнал без разрыва фазы) Таким образом, измерение разности f - fo - это и есть та операция, которую должен осуществлять детектор В Приложении 1 показано, что при наличии отсчетов квадратур исходного радиосигнала 5к и Ск и , к = О, 1, 2 и т д , величина может быть вычислена следующим образом 5 г +с: Отсюда вытекает структурная схема детектора, которая приведена на Рис. 5.8 Рис. 5.8. Цифровой частотный детектор x}-0-h( - ЮО)к (Sk+C,)- Следует отметить преимущества предлагаемого алгоритма демодуляции ЧМ-сигнала ♦ детектор не требует точной настройки квадратурного генератора (рис 1) на частоту fo, что позволяет ему устойчиво функционировать при значительных (до 30%) уходах частоты входного сигнала вследствие эффекта Доплера, ♦ операция деления на двучлен Зк + Ск не является обязательной, если динамика входного сигнала невелика, либо стабилизация амплитуды осуществляется при помощи АРУ в ВЧ-тракте, ♦ инвариантность алгоритма к фазе опорного и входного сигналов, а также к амплитуде входного сигнала (при наличии нормирующего множителя) увеличивает помехоустойчивость. При достаточно больших отношениях сигнал/шум (ОСШ) на входв демодулятора (20 30 дБ) восстановленную последовательность символов можно снимать непосредственно с выхода детектора Однако при снижении ОСШ (до 10...15 дБ) форма сигнала на выходе детектора начинает искажаться (появляются ложные перепады, смещение фронтов по времени и т п ) Поэтому на выход детектора (внутри ПЛИС) подключается еще один блок - синхронизатор, предназначение которого - восстановить истинную форму демодулированного радиосигнала за счет его накопления и анализа в течение N подряд идущих символов (в описанной далее версии демодуляторов N = 10) Синхронизатор реализует оптимальный (по критерию максимума правдоподобия) алгоритм оценки сигнала прямоугольной формы на фоне белого гауссовского шума Восстановлению подлежат истинные моменты смены символов в исходном радиосигнале (тактовая синхронизация), а также истинная полярность символов Главными элементами синхронизатора (Рис. 5.9) являются линия задержки на N х М отсчетов (М- чиспо отсчетов на символ) и (N + 1) сумматоров, реализующих операцию накопления Синхро- Рис. 5.9. Цифровой синхронизатор input -О- -Г siQ О mod О sign О L mod О :- I sign О L. mod О -, - JT symbO symb-1 symb -N sync низатор функционирует следующим образом каждый отсчет входного сигнала порождает сдвиг в линии задержки, после чего вычисляются суммы каждых М подряд идущих отсчетов, определяются их модули и производится усреднение результатов по N суммам (символам). Если в какой-то момент времени каждое суммирование (по М отсчетам) будет производиться внутри одного символа, значение усредненного сигнала будет максимальным, на выходе порогового устройства появится синхроимпульс, и в этот же момент будут считаны знаки накопленных сумм, с высокой вероятностью совпадающие с полярностями символов К преимуществам предлагаемого алгоритма следует отнести ♦ высокую эффективность (устойчивость к помехам, к уходу частоты следования символов от номинальной, к снижению частоты дискретизации и др ), ♦ способность точно восстанавливать моменты смены символов во входном сигнале при длинных (до N - 1 включительно) сериях нулей и единиц , причем в конце серии отсутствует переходный процесс (направленный на устранение накопленной ошибки), что характерно для аналоговых устройств, ♦ наличие на выходв демодулятора одновременно N подряд идущих символов, что может быть важно при корреляционной обработке потока данных (например, при поиске синхро-посылок), ♦ простоту операций (суммирование, сдвиг) и хорошую адаптацию к реализации на базе ПЛИС, что не характерно для большинства традиционных алгоритмов, содержащих петли обратной связи (синхронизатор с запаздывающим и опережающим стробированием и др.) Реализация цифровой части алгоритма демодуляции и выделения синхроимпульса была выполнена на кристалле Altera FLEX10K50. Реализованное устройство состоит из входных цифровых КИХ-фильтров с восемью отводами, непосредственно блока демодуляции сигнала и бпока синхронизатора. Для реализации входных КИХ-фильтров был использован пакет Altera DSP Design Kit. Данный пакет был выбран ввиду того, что он позволяет по рассчитанным коэффициентам цифрового фильтра быстро получить AHDL описание устройства с данными характеристиками и максимально доступной точностью при заданных значениях точности входных данных и внутреннего представления коэффициентов фильтрации Для этого исходные коэффициенты

|

|

© 2000 - 2025 ULTRASONEX-AMFODENT.RU.

Копирование материалов разрешено исключительно при условии цититирования. |