|

|

|

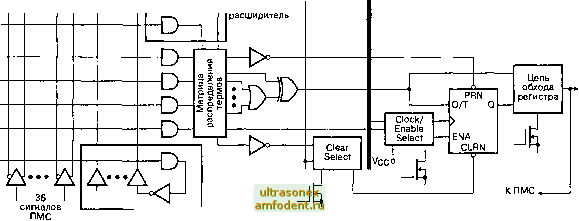

Главная страница Автономные управляющие системы - логические расширители (expanders) (параллельный (parallel) и разделяемый (shareble)); - программируемая матрица соединений (ПМС) (РпэдгаттаЫе interconnect array, PIA); - элементы ввода-вывода (ЭВВ)(1/0 control block) ПЛИС семейства МАХЗООО имеют четыре вывода, закрепленных за глобальными цепями (dedicated Inputs) Это глобальные цепи синхронизации сброса и установки в третье состояние каждой макроячейки Кроме того, эти выводы можно использовать как входы или выходы пользователя для быстрых сигналов, обрабатываемых в ПЛИС. Как видно из Рио. 1.1 в основе архитектуры ПЛИС семейства МАХЗООО лежат логические блоки, состоящие из 16 макроячеек каждый Логические блоки соединяются с помощью программируемой матрицы соединений Каждый логический блок имеет 36 входов с ПМС. На Рио 1.2 приведена структурная схема макроячейки ПЛИС семейства МАХЗООО МЯ ПЛ ис семейства МАХЗООО состоит из трех основных узлов - локальной программируемой матрицы (LAB local array), - матрицы распределения термов (product-term select matnx), - программируемого регистра (Programmable register) Комбинационные функции реализуются на локальной программируемой матрице и матрице распределения термов, позволяющей объединять логические произведения либо по ИЛИ (OR), либо по исключающему ИЛИ (XOR) Кроме того, матрица распределения термов позволяет скоммутировать цепи управления триггером МЯ Режим тактирования и конфигурация триггера выбираются автоматически во время синтеза проекта в САПР MAX+PLUS II в зависимости от выбранного разработчиком типа триггера при описании проекта в ПЛИС семейства МАХЗООО доступно 2 глобальных тактовых сигнала, что позволяет проектировать схемы с двухфазной синхронизацией Для реализации логических функций большого числа переменных используются логические расширители Рио. 1.3. Раздаляамый логичаокий раоширитель

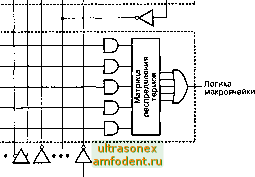

. Логика макроячейки  36 I I 16 сигналов разделяемых ПМС расширителей Разделяемый логический расширитель (Рио.1.3) позволяет реализовать логическую функцию с большим числом входов, позволяя объединить МЯ, входящие в состав одного ЛБ. Таким образом, разделяемый расширитель формирует терм, инверсное значение которого передается матрицей распределения термов в локальную программируемую матрицу и может быть использовано в любой МЯ данного ЛБ Как видно из Рис. 1.3, имеются 36 сигналов локальной ПМС, а также 16 инверсных сигналов с разделяемых логических расширителей, что позволяет в пределах одного ЛБ реализовать функцию до 52 термов ранга 1 Рис. 1.2. Структурная охема макроячайки ПЛИС оемейотва МАХЗООО Глобальный Глобальный сигнал сигнал сброса синхронизации Параллельный  кэвв Разделяемый расширитель Рис. 1.4. Параллельный логический расширитель предыдущей МЯ сигналов ПМС разделяемых расширителей

. Логика макроячейки . Логика макроячейки Параллельный логический расширитель (Рис. 1.4), позволяет использовать локальные матрицы смежных МЯ для реализации функций, в которые входят более 5 термов Одна цепочка параллельных расширителей может включать до 4 МЯ, реализуя функцию 20 термов Компилятор системы MAX+PLUSII поддерживает размещение до 3-х наборов не более чем по 5 параллельных расширителей. На Рис.1.5 приведена структура программируемой матрицы соединений Рис. 1.5. Структура ПМС ПЛИС семейства МАХЗООО Сигналы ПМС На ПМС выводятся сигналы от всех возможных источников ЭВВ, сигналов обратной связи ЛБ, специализированных выделенных выводов. В процессе программирования только необходимые сигналы заводятся на каждый ЛБ На Рис 1.5 приведена структурная схема формирования сигналов ЛБ Рис. 1.6. Элемент ввода-выводе -Е -Е -Е -С -С -С 6 глобальных сигналов разрешения выхода Мультиплексор разрешения выхода к другим выводам Vcc6 ОтМЯ. Выход открытый коллектор. Управление скоростью. кпмг. переключения На Рис 1.6 приведена схема элемента ввода-вывода ПЛИС семейства МАХЗООО. ЭВВ позволяет организовать режимы работы с открытым коллектором и третьим состоянием ПЛИС семейства МАХЗООО полностью поддерживают возможность программирования в системе в соответствии со стандартом IEEE Std 1149.1 - 1990 (JTAG) с использованием соответствующих инструментальных средств. Повышенное напряжение программирования формируется специализированными схемами, входящими в состав ПЛИС семейства МАХЗООО, из напряжения питания 3 3 В Во время программирования в системе входы и выходы ПЛИС находятся в третьем состоянии и слегка подтянуты к напряжению питания Сопротивления внутренних подтягивающих резисторов порядка 50 кОм. На Рис. 1.7 приведены временные диаграммы программирования ПЛИС семейства МАХЗООО через порт JTAG Рис. 1.7. Временные диаграммы программирования плис семейства МАХЗООО через порт JTAG TMS )С TDI- Захват Управление tjcp tjCH tjpzx tjszx tjCL tjssu tjpsu tjPH IJPCO IJSCO tjpxz tjSH tjsxz Значения временных параметров приведены в Таблице 1.2 Таблица t .2. Временные параметры порта JTAG

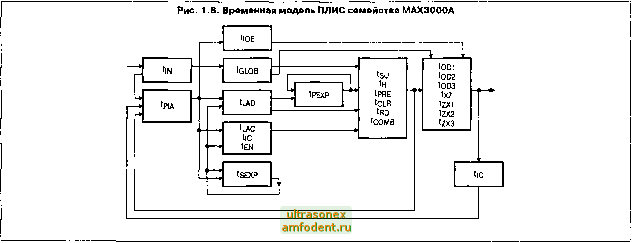

Временная модель ПЛИС семейства МАХЗОООА приведена на Рис 1.8 плис семейства МАХЗОООА имеют предсказуемую задержку распространения сигнала, поэтому результаты временного моделирования в САПР MAX+PLUS II полностью адекватны поведению реальной схемы, в отличив от ПЛИС, выполненных по SRAM технологии В Таблице 1.3 приведено описание параметров временной модели для ПЛИС семейства МАХЗОООА с быстродействием -4 и -10

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2000 - 2025 ULTRASONEX-AMFODENT.RU.

Копирование материалов разрешено исключительно при условии цититирования. |