|

|

|

Главная страница Автономные управляющие системы Таблица 1.7. Параметры временной модели (продолжение)

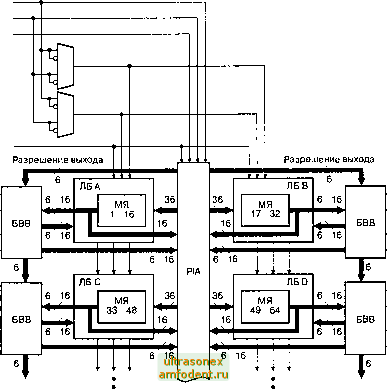

Бремене задержек распространения сигнала по ГМС приводятся из расчета худшего случая 1.3. СЕМЕЙСТВО МШООО ПЛИС семейства МАХ7000 являются первыми CPLD фирмы ALTERA, выполненными по технологии ПЗУ с электрическим стиранием (EPROM) В настоящее время выпускаются ПЛИС МАХ7000, МАХ7000А, МАХ7000В, МАХ7000Е, MAX7000S Семейства МАХ7000А и ГИАХ7000В рассчитаны на работу в системах с напряжением питания 3 3 и 2.5 В соответственно, ПЛИС MAX7000S является дальнейшим развитием 5-вольтового МАХ7000, с возможностью программирования в системв. В настоящее время это семейство, пожалуй, является самым популярным CPLD у российских разработчиков Это связано с тем, что для работы с ПЛИС этого семейства не требуется никаких серьезных затрат, поскольку пакет IAX-i-PLUS II BASELINE полностью поддерживает всех представителей огого семейства ПЛИС, а для программирования и загрузки конфигурации устройств опубликована схема кабеля ByteBlaster и ByteBlastelV В Таблице 1.8 приведены основные характеристики ПЛИС семейства MAX7000S Все ПЛИС MAX7000S поддерживают технологию программирования в системе (ISP, In-system programmability) и периферийного сканирования (boundary scan) в соответствии со стандартом IEEE Std 1149 1 JTAG Элементы ввода-вывода (ЭВВ) позволяют работать в системах с уровнями сигналов 5 В или 3 3 В. Матрица соеди- нений имеет непрерывную структуру, что позволяет реализовать время задержки распространения сигнала до 5 не ПЛИС MAX7000S имеют возможность аппаратной эмуляции выходов с открытым коллектором (open - drains pin) и удовлетворяют требованиям стандарта PCI Имеется возможность индивидуального программирования цепей сброса, установки и тактирования триггеров, входящих в макроячейку Предусмотрен режим пониженного энергопотребления Программируемый логический расширитель позволяет реализовать на одной макроячейке функции до 32 переменных Имеется возможность задания бита секретности (security bit) для защиты от несанкционированного тиражирования разработки В отличив от архитектуры МАХ7000 (рис. 1.22), ПЛИС MAX7000S (Рис. 1.23) имеют возможность использования двух глобальных тактовых сигналов На Рис. 1.24 приведена структура макроячейки логического элемента ПЛИС MAXIOQOS. Как можно заметить, МЯ ПЛИС МАХ7000 не отличается от МЯ МАХЗООО Аналогично ПЛИС семейства МАХЗООО, ПЛИС МАХ7000 имеют возможность использования параллельного и разделяемого расширителей, которые подробно описаны в параграфе 1 1 Таблица 1.8. Основные характеристики семейства MAX7000S

Рис. 1.22. Архитектура МАХ7000 INPUT/GCLK1 о-INPUT/GCLRn о-INPUT/OEIn о-INPUT/0E2n о- В...16 ; I/O PINS 8...16 ; I/O PINS * 8 .16 МЯ 1 16 36 16 8 16

МЯ 17. 32 В 16 8 .16 МЯ 49 .64 8 16 8 16 I 8 .16 I/O PINS ; 8...16 I/O PINS Рис. 1.23. Архитектура MAX7000S INPUT/GCLK1 о-INPUT/OE2/GCLK2 INPUT/0E1 о- INPUT/GCLRn о 6...16 ; I/O PINS 6...16 ; I/O PINS  ; 6...16 I/O PINS ; 6...16 I/O PINS Рис. 1.24. Структура макроячейки МАХ7000 36 сигналов ПМС Параллельный расширитель Глобальный сигнал Сброс синхронизации ? 5 о 16 сигналов с расширителей .К ЭВВ PRN ОД Q CLRN КПМС, .КЭВВ Рис. 1.25. Временная модель ПЛИС семейства МАХ7000 ~1 tN tPIA t0E(1) tGLOB tLrtD tPEXP tLAC tSEXP tFlN(1) tH tPRE tCLR tRD tCOMB tODI tOD2{2) tOD3 tZXl tZX2(2) tZX3(1) Ha Рис. 1.25 приведена временная модель ПЛИС семейства МАХ7000, а в Таблицах 1.9 и 1.10 ее параметры Таблица 1.9. Параметры временной модели МШООО (все времена в не)

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2000 - 2025 ULTRASONEX-AMFODENT.RU.

Копирование материалов разрешено исключительно при условии цититирования. |