|

|

|

Главная страница Автономные управляющие системы Рис. 5.13. Схема тестирования генератора ПСП rM eEew= i I.M1WIDTH.= 5J М(4..0) с1> М(4 0) I tn[.generate~ enable ! load[i:>

I 12 M2(tO..O) [ЦЭ L-,i M2(10 0) I m generate* ;M seeif) = ; I.MlWLDTH=.11J > out enable j clock ;

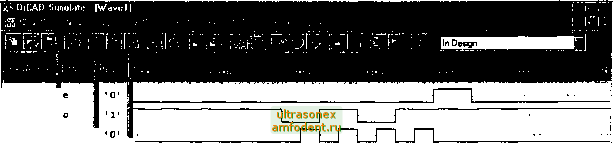

Файл M GENERATE.INC FUNCTION m generate (m[ {in width) - (1) 0], dk, gena, load) WITH (M WIDTH, M BEGIN) RETtJRNS (out) , Для моделирования работы генератора в графическом редакторе пакета MAX+PLUS II была создана тестовая схема, показанная на Рис. 5.13 Результаты моделирования показаны на Рис. 5.14 (на вход одного генератора подан характеристический многочлен М, = 11001, на входдругого - Ма = 10010000001) 5.5. ПРИМЕРЫ ОПИСАНИЯ ЦИФРОВЫХ СХЕМ НА VHDL Рассмотрим некоторые примеры описания L(ифpoвыx схем на VHDL Примером описания цифрового автомата является преобразователь параллельного кода в последовательный Преобразователь кода представляет собой устройство, на вход которого подается п-битное число в параллельном кодеd сигнал загрузки load и синхроимпульсы elk По сигналу загрузки происходит запись входного слова во внутренний регистр и последовательная выдача в течении п тактов этого входного слова в последовательном коде на выходе о синхроимпульсами oclk После окончания преобразования на выходе е появляется высокий уровень сигнала в течение одного такта Такого рода преобразователи кода часто используются для управления синтезаторами частот 1104ПЛ1 и им подобными Описание этого устройства на языке VHDL приведено ниже library leee, use ieee.std logic 1164 all, entity Serial is port ( elk . in STD LOQIC, load . in STD LOOIC; reset: in STD LOGIC; d in STD LOGIC veetor (3 dovmto 0) ; oelk : out STD LOGIC; out STD LOGIC; : out STD LOGIC end; architecture behavioral of Serial is type tl IS range 0 to 4, signal s : STD LOGIC vector (2 downto 0); signal 1 . tl; begin (elk) process begin if reset = Ч then 1 <= 0; else If (elkevent and clk=l) then If (1=0 and load = Ч) then s(2 dovmto 0) <= d(3 downto 1) , 0 <= d(0); 1 <= 4, end if. If (1 > 1) then 0 <= s(0) , s(l downto 0) <= s(2 downto 1), 1 <= 1 - 1; end if; If (i 1) then e <= Ч ; 1 < 0; else e <= 0, end If, end if; end If, If i>0 then oelk <= not elk; else oelk <= 0; end if; end process; end behavioral. По переднему фронту синхроимпульса elk при высоком уровне на входе загрузки происходит загрузка трех старших битов входного слова d(3 .1] во временный регистр s[2 0] Младший бит входного слова d[0] подается на выход о На выходе oclk появляются синхроимпульсы Сигнал Г выполняет функцию счетчика, выдаю-1цего сигнал окончания преобразования е При поступлении последующих синхроимпульсов происходит выдача на выход о остальных бит входного слова, хранящихся в регистре s[2 0] Моделирование этого устройства было проведено в системе проектирования OrCAD 9 О Для проверки схемы использовался тест library хаев; use ieee.std logic 1164.all; use ieee.numeric std.all; entity test serial is end test serial; architecture testbanch of test serial is cosponent serial port ( oik : xn 8td logxo; load : xn 8td logio; reset : xn 8td logio; d : xn 8td logxc vector (3 doimto 0) ; oclk : out 8td logio; о : out 8td logio; a ; out 8td logio end coiionent; Ha VHDL описание фильтра имеет вид-library ieee; use ieee.8td logio 1164.all; use ieee.8td logic arith.all; entity f is port ( din: xn 8td logio veotor(7 downto 0); 80ut: out 8td logxo veotor (15 doimto 0) ; r: in 8td logio; o: xn 8td logxo end f; architecture behavior of f is

Рис. 5.15. Результаты моделирования пресбрвзсввния кодов  test 3er test ser test sec: oclk test 3er; test ser test sec; d[3] d[2] d[l] d[0] reset load elk 10 0 0 0 0 0000 0000 jn rLXl Jn ri n rb FL n ri  (No vaiable data available] .....И11 Д1ш constant h21 00000010 ; constant h22 11111000 ; constant h23 11110101 ; std logxc vector (7 doimto 0) std logxc vector (7 doimto 0) std logxo vector (7 downco 0) signal xOO, xOl, x02, x03, x04, x05, x06, x07, x08, x09, xlO, xll, xl2, xl3, xl4, xl5, xl6, xl7, xl8, xl9, x20, x21, x22, x23 : std logio vector(7 downto 0); signal mOO, mOl, m02, m03, m04, m05, m06, m07, m08, m09, mlO, mil, ml2, inl3, inl4, ml5, ml6, ml7, ml8, ml9, m20, m21, m22, in23 : std logic vector (15 doimto 0); begin mOO < (slgned(xOO)*signed(h00)) mOl <> (signed(x01)*signed(h01)) m02 <>> (signed (x02)* signed (h02)) шОЗ < (signed(x03)*signed(h03)) m04 < (signed(x04)*signed(h04)) m05 < тОб <=: m07 <= m08 < m09 <>> mlO < mil < 11112 < ml3 < 11114 < ml 5 < ml 6 <-ml 7 < ml В < inl9 <> m20 <= ni21 < 11122 <> in23 < (signed(x05) (signed(x06) (signed(x07) (signed(x08) (signed(x09) (signed(xlO) (signed(xll) (signed(xl2) (signed(xl3) (signed(xl4) (signed(xl5) (signed(xl6) (signed(xl7) (signed(xie) (signed(xl9) (signed(x20) (signed(x21) (signed(x22) (signed(x23) *signed(b05)) *signed(hOe)) signed (h07)) *signed(b08)) *signed(h09)) signed(hlO)) signed(hll)) signed(hl2)) signed(hl3)) 8igned(bl4)) signed(hl5)) signed(hl6)) signed(hl7)) *signed(hl8)) signed(hl9)) signed(h20)) *signed(h21)) signed(h22)) 8igned(h23)) sout < (signed (mOO) -feigned (mOl) -feigned (m02) -fsignad (m03)

|

|

© 2000 - 2025 ULTRASONEX-AMFODENT.RU.

Копирование материалов разрешено исключительно при условии цититирования. |