|

|

|

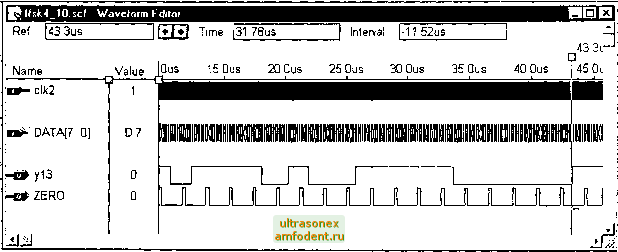

Главная страница Автономные управляющие системы фильтра масштабируются, что приводит к тому, что выходной сигнал фильтра таюке является промасштабированным на ту же величину, которую в большинстве случаев необходимо учитывать при дальнейших вычислениях Однако для данной задачи это не является существенным, и масштабирующий множитель не учитывался в последующих операциях. Кроме этого, DSP Design Kit позволяет сгенерировать векторный файл для моделирования работы фильтра, а также позволяет преобразовать выходные данные отклика фильтра к масштабу входных данных и построить график отклика фильтра на входное воздействие. Реализованный восьмиотводный фильтр имеет симметричную характеристику В отличие от классической реализации КИХ-фильтров в виде набора умножителей для взвешивания задержанных отсчетов входного сигнала и выходного сумматора, данная реализация вообще не содержит умножителей. Все операции умножения заменены операциями распределенной арифметики, что возможно благодаря постоянству коэффициентов фильтрации и наличию в логических элементах FLEX10K таблиц перекодировки (iook-up-tables, LUTs) Сигналы с выходов фильтров (восемь бит в дополнительном коде) подаются на квадратурные входы блока частотной демодуляции Для реализации демодулятора ЧМ-сигналов понадобились два регистра для хранения значений квадратур в предыдущий (к-й) момент времени - Зк и Ск, два умножителя и один сумматор Все вычисления в схеме производятся в дополнительном коде за исключением умножителей, операнды и выходные данные которых представлены в прямом коде со знаком, что требует предварительно преобразовывать сигналы в дополнительный код до умножения и конвертировать в дополнительный код результат умножения Выходной сигнал демодулятора имеет разрядность равную пятнадцати битам, однако для выделения символов нужно рассматривать только старший (знаковый) разряд результата Входным сигналом синхронизатора является выход блока демодулятора. Заметим, что для реализации суммирования вида зит, = у< + ук ,-нук 2+ +Ук-п-к нецелесообразно использовать каскад из п двухвходовых сумматоров, так как на каждом такте результат этого суммирования может быть получен из значения суммы на предыдущем такте путем вычитания yi< n-i и прибавления ук +1 А именно sumi., =зит, + Ук,.1 + Ук-г -Ук-п -1 Таким образом, для реализации этой части алгоритма синхронизации понадобится один регистр для хранения значения суммы на предыдущем такте и три сумматора, один из которых используется для изменения знака у значения Ук-п-i (так как все числа представлены в дополнительном коде) Кроме того, необходимы регистры для хранения значений Ук, Ук- ъ Ук -п +i Если же не учитывать эти п регистров, то количество элементов для выполнения такой операции суммирования не будет зависеть от количества операндов и можно сэкономить ячейки ПЛИС при количестве слагаемых в сумме п > 4 В данном же случае количество слагаемых в каждой сумме равно количеству отсчетов сигнала, приходящихся на символ, то есть п = 8 и эффект в увеличении скорости, а главное, в уменьшении занимаемого места, ощутим Блок сумматора был реализован в виде мегафункций, выходными сигналами которого являлись как значение суммы, так и значение Ук п -1. для удобства последовательного соединения таких блоков по входам, что необходимо виду того, что выходящее из одной суммы слагаемое становится слагаемым следующей суммы Xk=nch (sum,) +nch(sumn.i + +Й1 ch (sum,*, ,) Так как синхронизатор работает по принципу максимума правдоподобия, то схема должна выставлять синхроимпульс в момент достижения выходным сигналом Хк максимума Для определения момента наступления локальных максимумов этот сигнал дифференцируется, и определяются моменты смены знака продифференцированного сигнала Результаты моделирования в системе Max+Plus II приведены на Рис. 5.10 В заключение отметим, что все узлы системы были реализованы в виде параметризованных мегафункций с использованием языка описания аппаратуры AHDL, что позволяет с легкостью их использовать для приложений, требующих другой точности вычислений Рис. 5.10. Результаты моделирования  Рис. 5.11. Генератор ПСП GENA . CLOCK M(M WIDTH-1) М(2) М(1) М(0) D Q >CLK Г СЕ 5 О Q >CLK СЕ 5 D Q >CLK СЕ 5 D Q >CLK Г СЕ 5 5,4. РЕАЛИЗАЦИЯ ГЕНЕРАТОРА ПСП НА ПЛИС Генератор формирования М-последовательностей был написан в виде параметризованной макрофункции, описывающей устройство, упрощенная структура которого показана на Рис. 5.11. Параметрами макрофункции являются длина характеристического многочлена и число, описывающее начальные состояния триггеров Ниже приводится листинг описания этой функции на AHDL Функция M GENERATE функция M GENERATE Генерирует М-последовательность, заданную характеристическим нногочленом М MIM WIDTH-1..0] GENA LOAD VARIABLE dffs[M WIDTH-2..0] регистра сдвига shift node[M WIDTH-2..0) xor node[M WlDTH-2..0] shiftin, shiftout вход и выход регистра сдвига INPUT = GND; : INPUT; INPUT = GND; INPUT = GND; ; OUTPUT; DFFE; - триггеры NODE; NODE; : NODE; - Входы M GENA CLK LOAD Выходы OUT - вход многочлена, - разрешение генерации (de£aulb=GND) ; - тактовый вход, - вход предустановки (default=GND), - выход М-последовательности IF (USED(M BEGIN)) GENERATE ас . lpin constant WITH (LPM WIDTH = M BEG11J) , END GENERATE, BEGIN M WIDTH, LPM CVALUE Параметры M WIDTH M BEGIN % Версич 1 0 длина полинома; начальное состояние ldefault= 100000 .00 ), INCLUDE lpin xor.inc , INCLUDE lpin constant. inc PARAMETERS ( M WIDTH, M BEGIN = 0 SUBDESIGN in generate ( ASSERT (M WIDTH>0) REPORT Значение параметра MWIDTH должно быть больше нуля SEVERITY ERROR; общие выводы триггеров dffst).епа = GENA; dffst].oik = CLK; асинхронные операции IF (USED (M BEGIN) ) GENERATE dffst] elm = load # ac. result tM WIDTH-2.. 0]; % установка начального состояния % dffs[].prn= load* ac.resulttM HlDTH-2..0]; % триггеров, заданное M BEGIN % ELSE GENERATE dffs[M MIDTH-3..05.clrn = load; % установка начального состояния % dff8[M WIDTH-2].ргп = load; % фриггвроа 10000..00 KNO GENERATE; обратные связи xor node[] dff8[] £ М[M WIDTH-2..о]; hiftin - lp xor(xor nodeI3) WITH (LPM SIZK M WIDTH-1, LPM WIDTH 1) ; операции сдвига hift noden - (ehiftin, dffe[M WIDTH-2. .1]); shiftout = d£fs[0]; синхронные операции d££s[].d = load i shift node[]; подключим выход OUT shiftout; END; Описание Функции. Входы: Рис. 5.12. Символ генераторв ПСП Гм ЛТбтн=1 m generate I M BEGIN =

OUT M - шина (группа выводов) с размером M WiDTH На этот вход подаются коэффициенты характеристического многочлена, CLK - вход тактового сигнала, GENA -вход разрешения генерации ПриОЕМА = 0 генерация М-последовательности запрещена, LOAD - вход предустановки При LOAD = Г триггеры регистра сдвига устанавливаются в состояние, определяемое параметром M BEGIN, Выходы OUT - выход М-последовательности Для включения данной функции в другие схемы были также созданы включаемый файл, содержащий описание, и графический символ-элемент (см Рис. 5.12) Рис. 5.14. Результаты моделирования генератора ПСП *5fMAX<plus II Untilledl (ml scf Wavefotm Editoi) MX+Plus II Be £( ifiew Mode fissign ЦШю Qptions №dow tlelp I Inleivai 29 68us load enable ш#~ clock Ref lODns Name g 0 0ns [10 0] J4j Time 5 0us 29 68us 1Q0us 15 0us 20 0us m[4 0]p 11001 out 0 25 Ous

|

|||||||||||||||||||||||||||||||||

|

© 2000 - 2025 ULTRASONEX-AMFODENT.RU.

Копирование материалов разрешено исключительно при условии цититирования. |