|

|

|

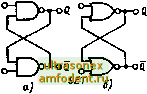

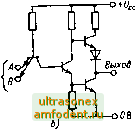

Главная страница Фундаментальные понятия электротехнологии Логическая функция Буфер Инвертор (НЕ) И-не ИЛИ-НЕ Исключающее ИЛИ Стандарт США -> Стандарт Вепикобритании BS3S3 А-В- Таблица истинности Рис. 6.2. Символы логаческих элементов и таблицы истинности Логическая схема ИЛИ Она осуществляет операцию логического сложения сигналов. На выходе схемы присутствует логическая 1 в том случае, если логическая 1 есть хотя бы на одном иэ входов. Сигнал О на выходе появляется тогда, когда на всех входах одновременно присутствует логический 0. Логическая схема И-НЕ Сигнал на выходе зтой схемы является инвертированным выходным сигналом схемы И. Если на всех входах схемы И-НЕ, присутствует ло гическая 1, то на выходе будет 0. Любая другая комбинация входных сигналов обусловливает появление логической 1 на выходе схемы. 106 Логическая схема ИЛИ-НЕ Сигнал на выходе зтой схемы является инвертированным выходным сигналом схемы ИЛИ. Если на всех входах схемы ИЛИ-НЕ имеется логический О, то на ее выходе логическая 1. Любые другие комбинации входных сигналов обусловливают появление логического О на выходе схемы. Логическая схема исключающее ИЛИ Эта схема имеет на выходе логическую 1, если на одном из ее входов имеется логическая 1, а на другом - 0. Бели же на обоих входах схемы пртсутствуют логический О или логическая 1, то на выходе будет 0. Ждущий мультивибратор Логическая схема с одним устойчивым состоянием на выходе называется ждущим мультивибратором. Выходной сигнал зтой схемы равен 0 до тех пор, пока на ее вход не поступит сигнал запуска. Срабатывание микросхемы происходит либо при изменении входного сигнала от О к 1 (положительный фронт), либо при изменении входного сигнала от 1 к О (отрицательный фронт). Обычно микросхема имеет два соответствующих входа. В момент срабатывания выходной сигнал изменяется от О к 1. Время сохранения высокого уровня сигнала на выходе определяется внешней ЯС-цепью. Затем выходной сигнал снова становится равным О и схема ждет прихода следующего сигнала запуска. Примером такой микросхемы из серии ТТЛ является схема 74121 (рис. 6.3). Этот ждущий мультивибратор может срабатывать как от положительного, так и от отрицательного фронта запускающего сигнала и имеет два комплементарных выхода Q н Q.K. микросхеме требуется присоединить один внешний резистор и один внешний конденсатор. Входы микросхемы А1, А2 и В для выбора режима запуска могут быть соединены следующими тремя снособами: Времязадаюи1ие компоненты у--л-, 1 ] [ 1 J] [?1 Рис. 6.3. Внутренняя структура одновибратора 74121 Ш Ы Ш ЙШ l£j lil AI AZ в Q О Входы 1) если входы Л1 и А2 присоединены к логическому О, то запуск схемы осуществляется положительным фронтом по входу 5; 2) если входы AI и В присоединены к логической 1, то запуск схемы осуществляется отрииателькым фронтом по входу А2; 3) если входь! А2 п £ присоединены к логической то запуск схемы осуществляется отрицательным фронтом по входу А1. Аналогом микросхемы 72121 является микросхема К155АГ1. Небольшие замечания и советы Запущенный ждущий мультивибратор 74121 нечувствителен к входным сигналам А1, А2, В. Повторно его можно запустить по истечении временного интервала, равного длительности сформированного сигнала. Минимальная длительность запускающего сигнала ждущего мультивибратора 74121 равна 50 не. Максимальная длительность выходного сигнала может составлять несколько секунд. Сопротивление используемых резисторов изменяется в пределах от 1,5 до 47 кОм. Максимальное значение емкости конденсатора ограничивается лишь его током утечки и может составлять несколько сот микрофарад. Триггер Триггер имеет на выходе два устойчивых состояния: О или 1. Установившийся уровень выходного сигнала сохраняется сколь угодно долго до момента прихода следующего запускающего сигнала. Ниже описаны некоторые разновидности триггеров. /г-5-триггер Это самая простая разновидность триггера (рис. 6.4). Устройство имеет два входа: установление {SET) в состояние 1 и восстановление {RESET) в состояние О и два комплементарных выхода Q и Q. Сигнал логической 1, поданный на вход 5,вызьшает (или подтверждает) сигнал RESET RESET  Рис. 6.4. R-S-триттер на основе схем: а ~ И-НЕ; ff- ИЛИ-НЕ Рнс. 6S. Символы триггеров R-S-(flJ.D- (в) иУ-АГ-типов (в) логической 1 на входе Q. Тот же сигнал на входе R вызывает (или подтверждает) логический О на выходе Q. С другой стороны, триггер сохраняет свое установившееся состояние вплоть до прихода следующего входного сигнала. Л диггер Триггер этого типа имеет два входа: информационный входили вход задержки (delay) и тактовый вход Т. Сигнал логического О на входе D вызывает (или подтверждает) состояние логического О на выходе триггера в тот момент, когда на входе Г появляется тактовый сигнал, соответствующий логической 1- Если на входе D появляется логическая 1, то на выходе логическая 1 устанавливается опять-таки в момент прихода тактового сигнала на вход Т. Таким образом, при логической 1 на входе Г в триггер записывается информация, соответствующая информации на входе D, т.е. триггер вьшолняет функцию элемента задержки на один такт. В устройстве могут быть предусмотрены дополнительные вспомогательные входы, которые позволяют устанавливать или восстанавливать на выходе прибора 1 или 0. Они обычно иаэьшаются PRESET {PR) и CLEAR (очищающий - CLR). Триггеры С-типа используются в качестве элементов памяти или двоичных делителей частоты. /-/-триггер У--триггер имеет два тактовых входа {J и К), два прямых входа {PRESET и CLEAR) , счетный вход CLOCK {СК) и два комплементарных выхода Q ч Q. При установлении логического О иа входах PR или СК на выходе Q устанавливаются соответственно 1 или О. Символы триггеров различных типов показаны на рис. 6.5. Небольшие замечания и советы Л-5-1риггер может быть легко реализован путем соединения логических схем ИЛИ-НЕ, а также И-НЕ, как показано на рис- 6.4. Для этого триггера запрещена комбинация входных сигналов R = 1 и 5 = 1. При этом состояние выходов схемы может быть любым. J-A-триггер обладает наибольшими функциональными возможностями по сравнению с другими типами триггеров. Семейства логических элементов Цифровые интегральные схемы принято классифицировать в соответствии с технологией их изготовления. Семейство, к которому принадлежит микросхема, характеризует времена ее переключения, помехоза- Входы -IS Ы ОВыход Входы  Рис. 6.6. Структура двухвхоцовых схем И: д - КМДП-логика; ff - ТТЛ Пример 6.2. Обозначение 4001UBE обозначает, что это улучшенная (без буфера) версия 4001 прибора. Интегральная микросхема 74LS14 является маломощной с транзисторами Шотки версией прибора ТТЛ серии 7414. Характеристики логической микросхемы Логические уровни - это диапазон напряжений, используемый для представления логического О или 1. Логические уровни КМДП-микро-схем заметно отличаются от уровней ТТЛ. В частности, логические уровни КМДП-микросхем определяюхся относительно значения питающего напряжения, а уровни ТТЛ-микросхем не зависят от него. Б табл. 6.3 приведены ориентировочные значения выходных напряжений логических микросхем. щищенность, потребляемую мощность и т.п. Речь идет о двух принщ1-ниально разных технологиях. Первое семейство микросхем основано на использовании биполярных приборов и называется транзисторно-транзисторной логикой (ТТЛ), а второе семейство микросхем основано на использовании полевых комш1ементарных транзисторов с изолированным затвором (КМДП). На рис. 66 приведены примеры двухвходовых микросхем типа И, относящихся к семействам КМДП-логики и ТТЛ. Серия 74 является наиболее часто используемой разновидностью ТТЛ Приборы этой серии имеют маркировку, в начале которой указан номер 74. Варианты приборов внутри этой серии устанавливаются с но-мощью буквы, находящейся за номером 74; нет буквы - стандартный ТТЛ-прибор; С - КМДП-анапог ТТЛ-прибора; F - быстродействующий прибор; Н - быстродействующий прибор; S - прибор с транзисторами Нютки (улучшены быстродей- ствие и помехозащищенность); LS - маломощный прибор с транзисторами Шотки; НС - быстродействующий КМДП-аналог ТТЛ-прибора (входы совместимы с КМДП-погикой) ; нет - быстродействующий КМДП-аналог ТТЛ-прибора (входы совместимы с ТТЛ). Наиболее распространенной для КМДП-погики является серия 4000. Приборы этой серии маркируются с помощью следующих букв: нет буквы - стандартный КМДП-прибор; А - стандартный (без буфера) КМДП-прнбор; В, BE - улучшенный (с буфером) КМДП-прнбор; ив, иВЕ - улучшенный (без буфера) КМДП-прнбор. Таблица 6.3. Значение выходных напряжений логических микросхем Сигнал Тип микросхемы КМДП Логическая 1 Логический О Неопределенность oixiwd до 21Юаа >2В <0,8В От 0,8 до 2 В Примечание. U - напряжение питания КМДП-микросхем. Помехоустойчивость логического прибора - это мера его способности не реагировать на сигнал помехи. Чем выше запас помехоустойчивости, тем лучше приспособлен прибор к работе в условиях повышенного уровня шума. Запас помехоустойчивости определяется как разность минимального значения высокого уровня выходного напряжения (t/g нимального значения входного напряжения, соответствующего уровню логической 1,т. е. пом вых min Bxrain- Запас помехоустойчивости по низкому уровню определяется как разность максимального значения низкого уровня выходного напряжения и максимального значения входного напряжения, соответствующего уровню логического О, т. е. дггО г/О trO -пом su-x.max -шхтах-

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2000 - 2025 ULTRASONEX-AMFODENT.RU.

Копирование материалов разрешено исключительно при условии цититирования. |